Next generation semiconductor devices and applications

# (차세대 반도체 소자 및 응용)

### 장소: 공과대학 6호관 510호 시간: 화 (6-A, 6-B, 7-A, 7-B, 8-A, 8-B)

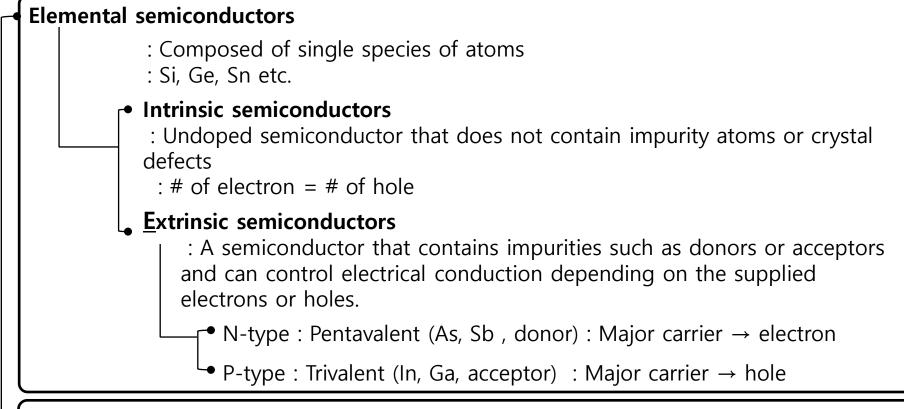

### **Classification of Semiconductor**

#### **Compound Semiconductors**

- : Composed of two or more elemental compounds

- : III-V compound (GaAs, GaP, InP, InAs, GaN etc.)

- : II-VI compound (ZnO, CdS, ZnTe etc.)

- : IV-VI compound (PbS) & IV-IV compound (SiC)

#### **Intrinsic Semiconductor**

| TABLE 12-2<br>A Summary of Band-Gap Ene                                               | ergies for Semico | nducting Materials |

|---------------------------------------------------------------------------------------|-------------------|--------------------|

| General<br>Type                                                                       | Material          | Band Gap<br>(eV)   |

| IV                                                                                    | Si<br>Ge          | 1.1<br>0.68        |

| - Organic semiconductor<br>- Metal Oxide Semiconductor                                | AlSb<br>GaAs      | 2.4                |

| - 2D semiconductor                                                                    | GaSb              | 1.4<br>0.67        |

| II-VI<br>1 eV < E <sub>g</sub> < 2 eV                                                 | InP<br>InAs       | 1.25<br>0.33       |

|                                                                                       | InSb<br>ZnTe      | 0.18<br>2.1        |

|                                                                                       | CdSe<br>CdTe      | 1.7                |

| <ul> <li>Pure elements: Si, Ge</li> <li>Stoichiometric compound: GaAs, CdS</li> </ul> | CdS               | 1.5<br>2.4         |

| > stolenometre compound. eu/is, eus                                                   | HgSe              | 0.6                |

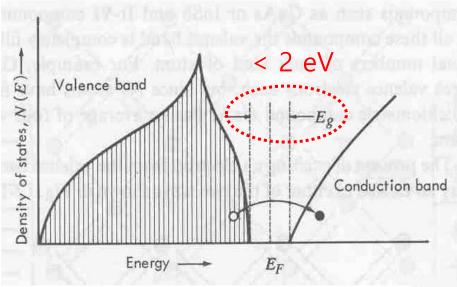

#### **Intrinsic Semiconductor**

Band structure of semiconductor

Devices LAB.

**Applied Nanom**

Electronics & Probes by Materials Engineerin

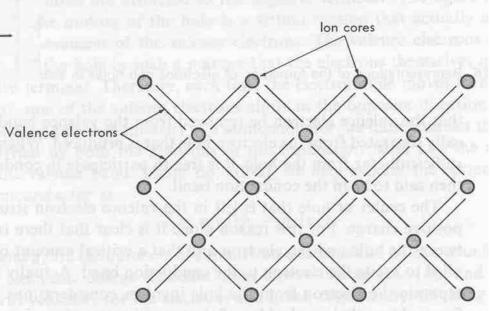

#### [Intrinsic semiconductor]

Valence electron : 4

G.14 : Si, Ge

Average valence electron : 4

III-V: GaAs, InSb II-VI: CdSe, ZnS

#### Covalent bond structure of Si

#### **Intrinsic Semiconductor**

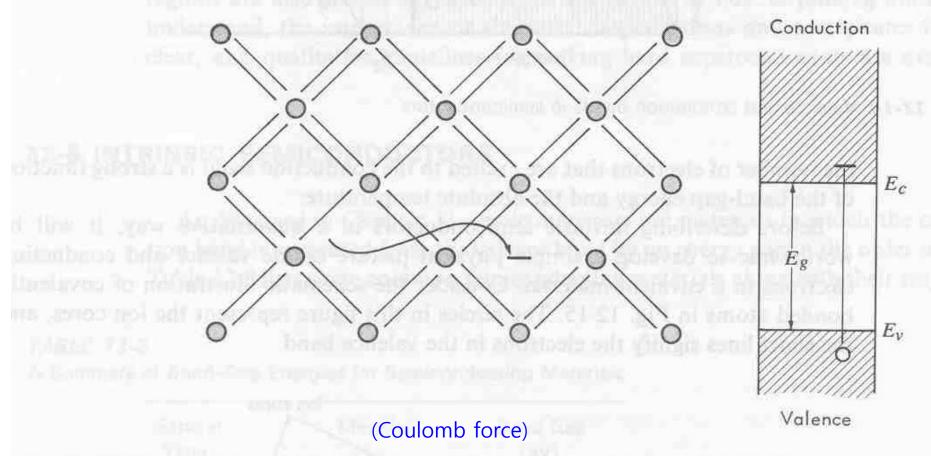

$\hfill\square$  Energy band gap( $E_q$  ) and  $\hfill$  Formation of electron-hole pair

FIG. 12-16 Representations of the formation of electrons and holes in semiconductors

#### **Intrinsic Semiconductor**

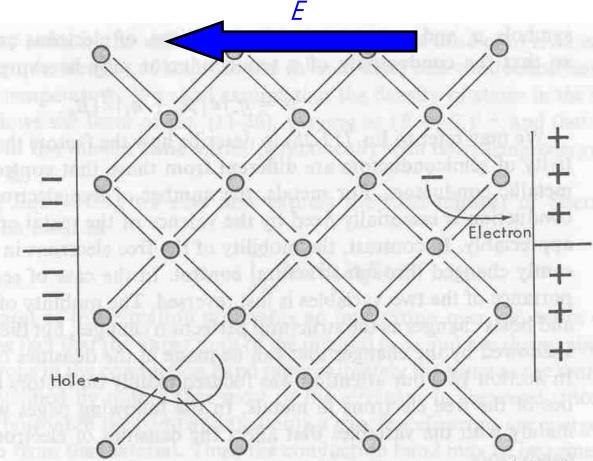

: Electric conduction in intrinsic semiconductor

Electric field (←)

Net direction of elec.  $(\rightarrow)$

Net direction of hole (←)

Current direction (←)

on by the migration of electrons and holes in response to applied voltage

Conduction of Semiconductor migration of i) electrons in the conduction band ii) holes in the valence band

#### The formula for electrical conduction in intrinsic semiconductors

$$J = \eta_{e} |e| v_{e} \text{ at conductor } J = current density \\ \eta \text{ (ita) = number of conduction elec. per unit vol.}$$

$$J = \eta_{e} |e| v_{e} + \eta_{h} |e| v_{h}$$

$$\int J = \sigma E \\ \sigma = J / E$$

$$\sigma = \eta_{e} |e| \left(\frac{v_{e}}{E}\right) + \eta_{h} |e\left(\frac{v_{h}}{E}\right)$$

Mobility (이동도)

$$\sigma = \eta_e |e| \mu_e + \eta_h |e| \mu_h$$

Applied Nanomaterials & Devices LAB. Electronics & Probes by Materials Engineering

Factors affecting the conductivity of semiconductors. : mobility, # of conduction elec. & hole per unit vol. of elec. & hole

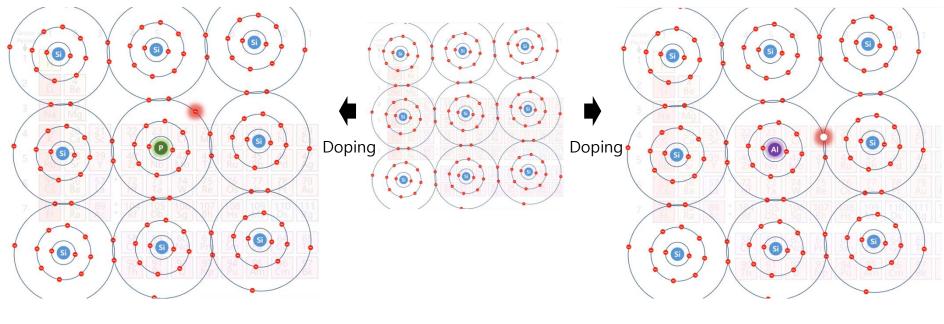

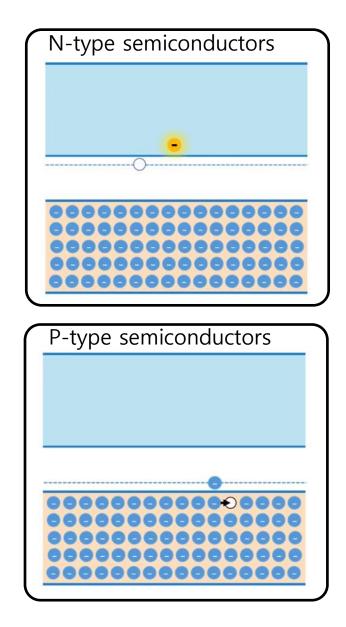

### **Extrinsic Semiconductor**

### Doping

- : Hole?

- The absence of an electron in a particular place in an atom.

- Virtual particle, Not a physical particle.

- Move through the lattice as electrons can.

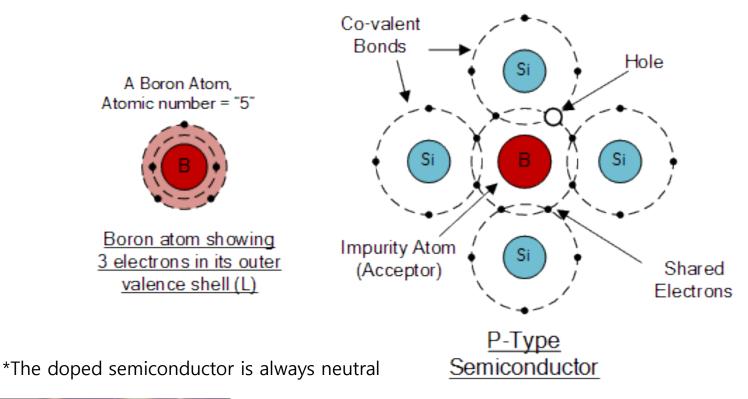

#### **Extrinsic Semiconductor**

→ Can control electrical conduction according to supplied electrons(donors) or holes(acceptors)

$\rightarrow$  5 group (donor) : n-type , 3 group (acceptor) : p-type

#### (a) n-type semiconductor

(b) p-type semiconductor

Group V: P, As, Sb,.. Major carrier  $\rightarrow$  electron

Applied Nanomaterials & Devices LAB. Electronics & Probes by Materials Engineering Group III: B, Al, Ga, In,... Major carrier  $\rightarrow$  hole

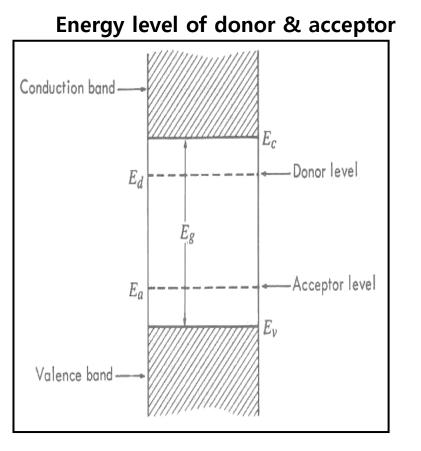

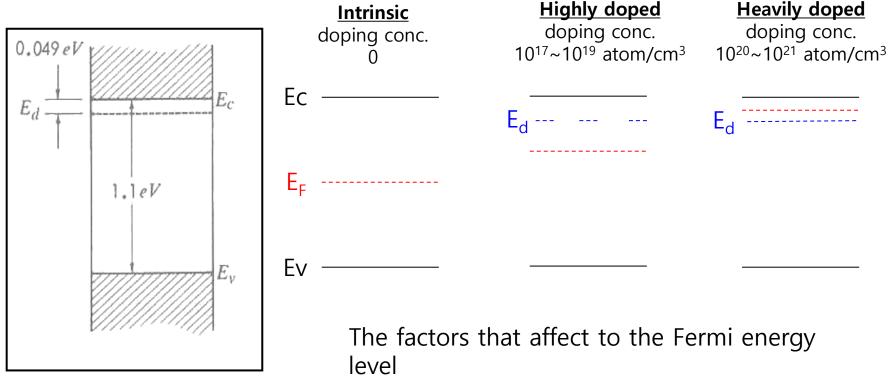

#### **Extrinsic Semiconductor**

Position of donor & acceptor level

Fig. 3-19 Donor and acceptor energy levels in semiconductors

#### **Extrinsic Semiconductor**

Position of donor & acceptor level

Energy level of donor & acceptor

# Conduction band- $E_c$ Donor level $E_d$ Acceptor level $E_{a}$ Eυ Valence band

Fig. 3-19 Donor and acceptor energy levels in semiconductors

#### Si : Energy level of donor & acceptor

| Donor Impurities |                  | Acceptor Impurities |                  |

|------------------|------------------|---------------------|------------------|

| Impurity         | $E_c - E_d$ (eV) | Impurity            | $E_a - E_v$ (eV) |

| Р                | 0.044            | В                   | 0.045            |

| As               | 0.049            | AI                  | 0.057            |

| Sb               | 0.039            | Ga                  | 0.067            |

| Li               | 0.033            | In                  | 0.16             |

#### **Ge** : Energy level of donor & acceptor

| Donor Impurities |                     | Acceptor Impurities |                  |

|------------------|---------------------|---------------------|------------------|

| Impurity         | $E_c - E_d \; (eV)$ | Impurity            | $E_a - E_v$ (eV) |

| Li               | 0.0093              | Zn                  | 0.029            |

| Р                | 0.012               | В                   | 0.0104           |

| As               | 0.0127              | Al                  | 0.0102           |

| Sb               | 0.0097              | Ga                  | 0.0108           |

| Bi 0.012         | 0.012               | In                  | 0.0112           |

|                  | Cu                  | 0.040               |                  |

\*kT<sub>300K</sub> = 0.0259 eV

#### Temp. dependence of carrier concentrations in Extrinsic semiconductor

In case, Si, dopant: As atoms (2 x 10<sup>21</sup>) -> n-type Si

] Temp. dependence of Fermi energy

Fig. 3-20 Energy levels in an n-type semiconductor and dependence of the Fermi energy on temperature

- i) Doping concentration

- ii) Absolute temperature

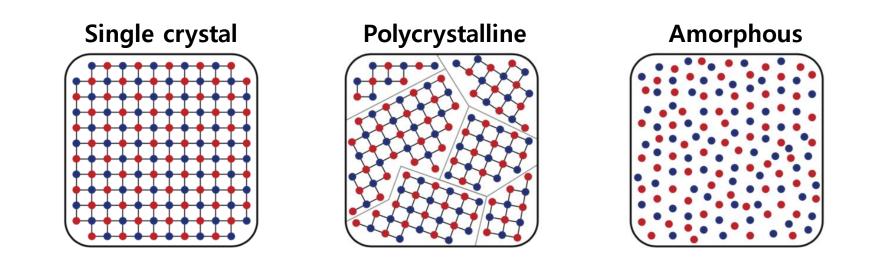

#### **Crystallinity of Silicon**

| Mobility              | High<br>600 cm²/Vs | Moderate<br>(~100 cm²/Vs) | Low<br>(1 ~ 10 cm²/Vs) |

|-----------------------|--------------------|---------------------------|------------------------|

| Resistance            | Low                | Moderate                  | High                   |

| Process<br>difficulty | High               | Moderate                  | Low                    |

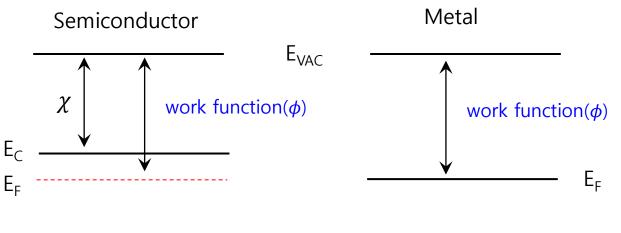

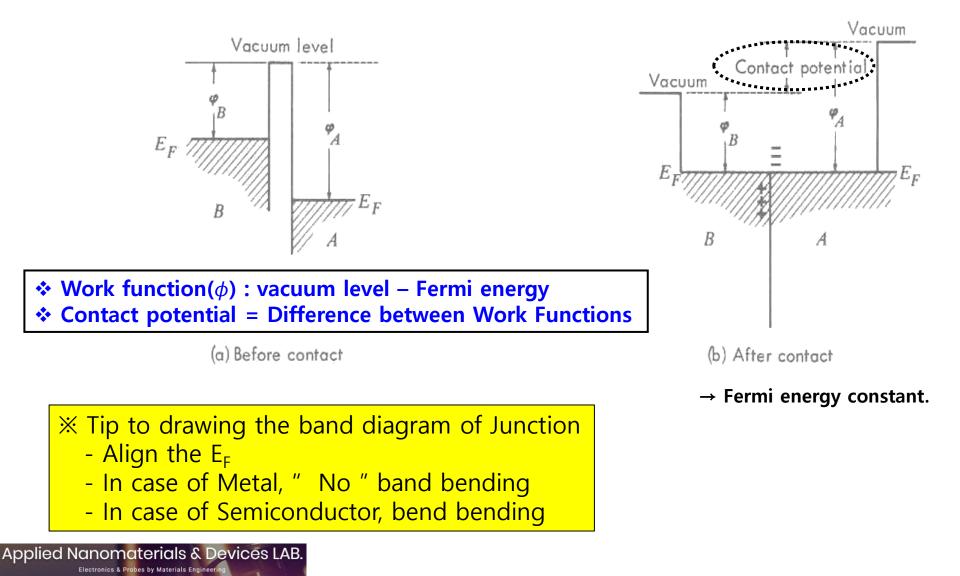

#### **Metal-Metal junction**

2-1. Property of Metal

E<sub>v</sub>

Electronics & Probes by Materials Engineer

evices LAB.

Applied Nano

- i) Energy bandgap = 0 eV

- ii) Can be regarded as N++ or P++ semiconductors

- iii) Excess carriers inside metals:  $L_{diff} = 0$ , lifetime = 0

- No excess carriers ( $\delta n \& \delta p = 0$ )

- Instant decay or recombination of excess carriers

- $\chi$  : The amount of energy released when an electron attaches to a neutral atom or molecule in the gaseous state to form an anion

- $\phi$ : The minimum energy needed to remove an electron from a solid to a point in the vacuum immediately outside the solid surface.

#### **Metal-Metal junction**

: The electron flow from a metal with a small work function to a metal with large work function

#### **Metal-Metal junction**

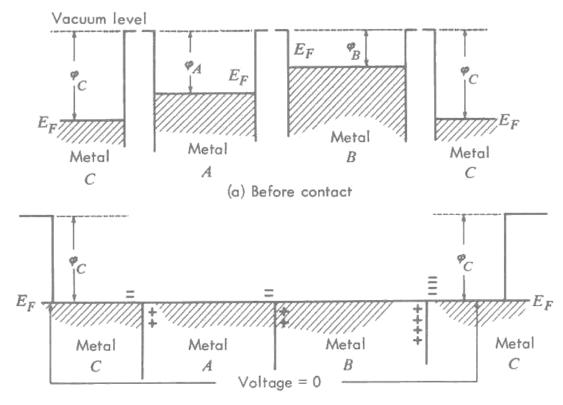

: Contact potential

(b) After contacts

$(\phi_C - \phi_A) + (\phi_A - \phi_B) + (\phi_B - \phi_C) = 0$

Contact voltages produced by contacting metals A and B with lead wire C. The voltage between the two ends of the lead wire is zero.

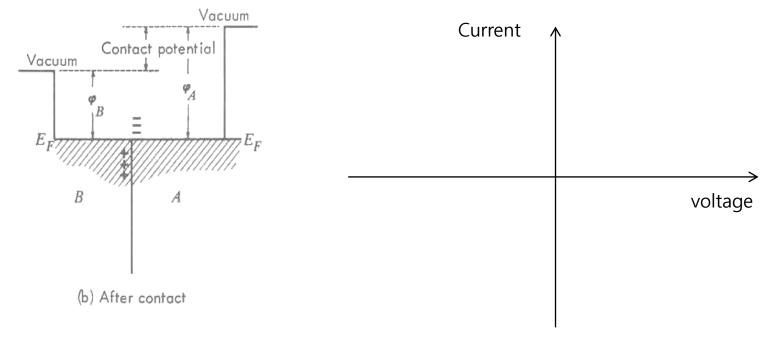

#### **Metal-Metal junction**

2-2. Electrical property of metal-metal contact

#### : Ohmic contact

> a junction between two conductors that has a linear <u>current-voltage</u> (I-V) curve as with <u>Ohm's</u> <u>law.</u>

> V = IR

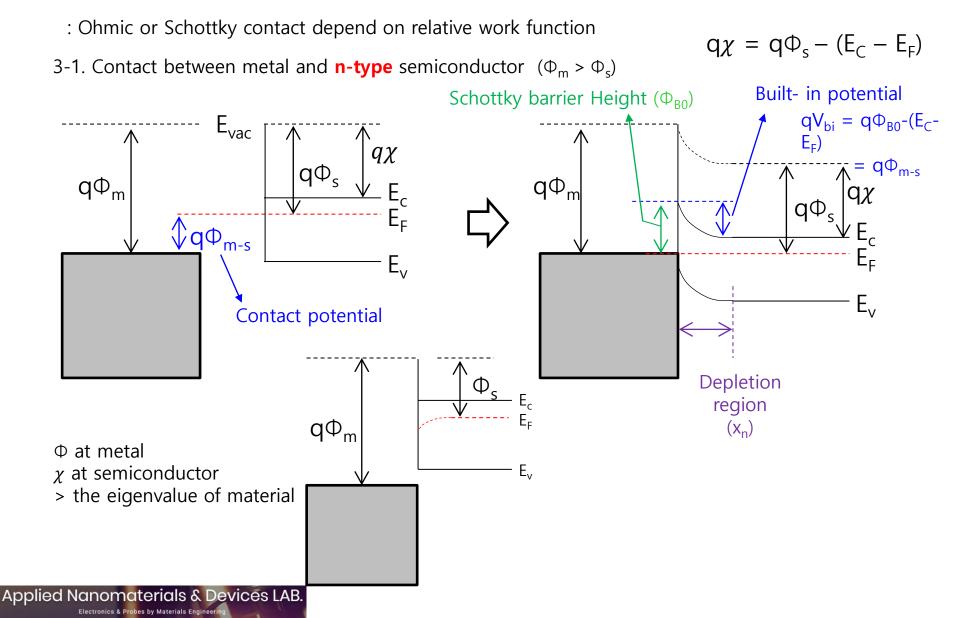

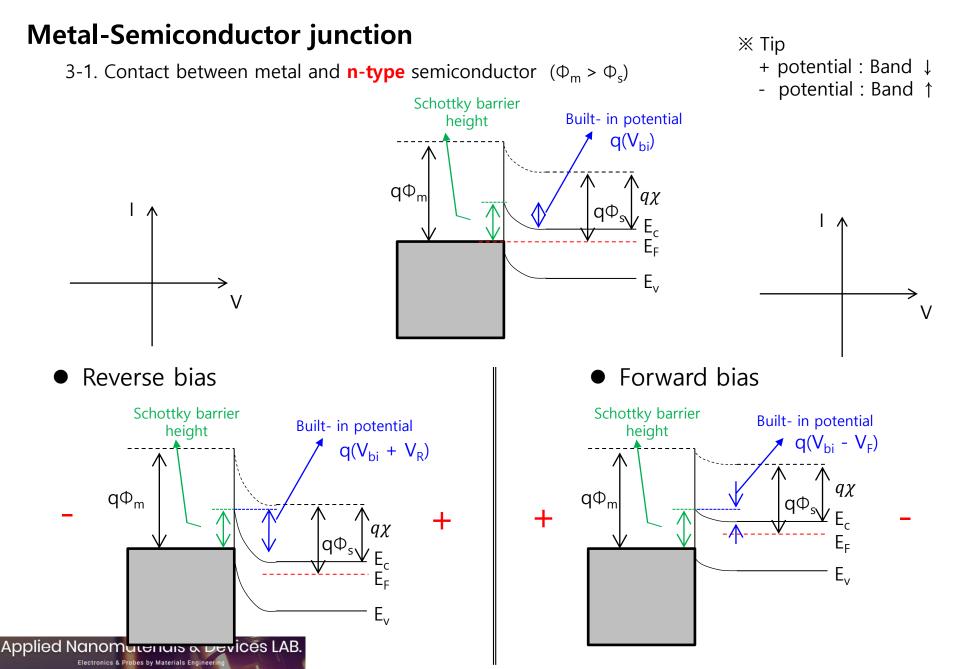

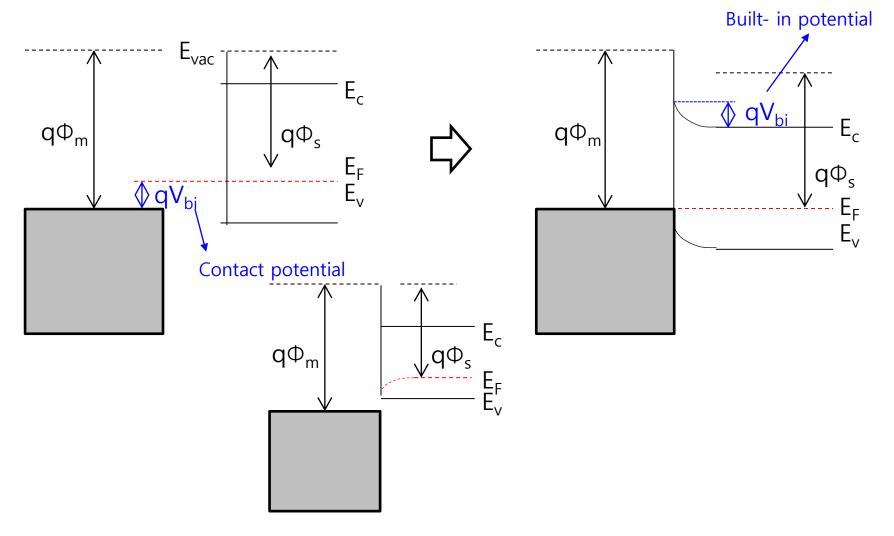

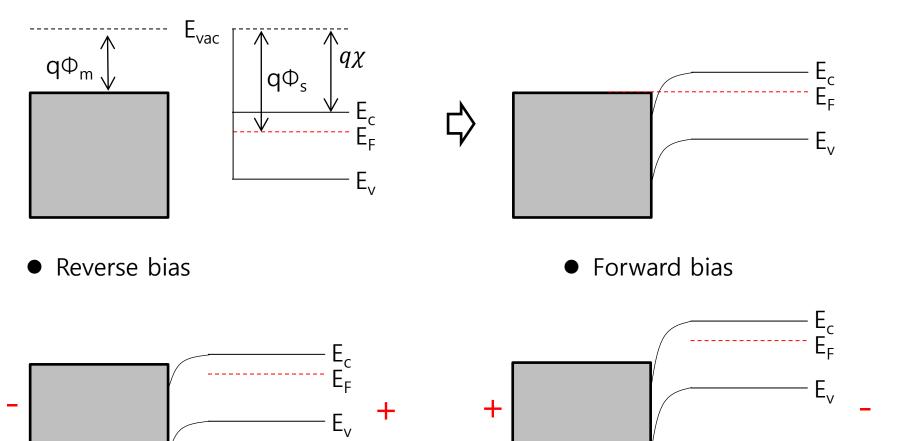

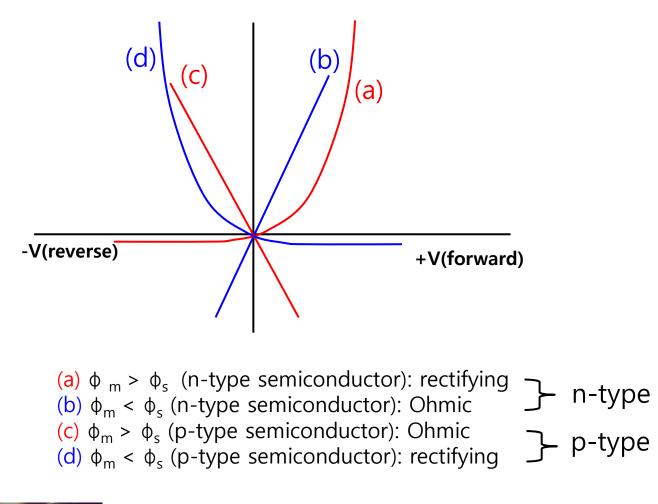

#### **Metal-Semiconductor junction**

#### **Metal-Semiconductor junction**

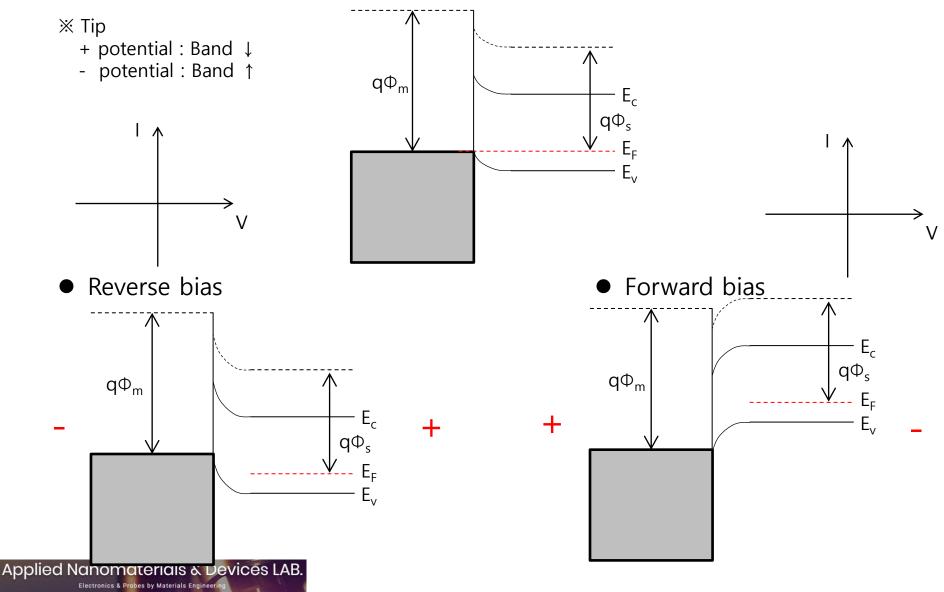

3-2. Contact between metal and **p-type** semiconductor  $(\Phi_m > \Phi_s)$

#### **Metal-Semiconductor junction**

3-2. Contact between metal and **p-type** semiconductor  $(\Phi_m > \Phi_s)$

#### **Metal-Semiconductor junction**

3-2. Contact between metal and **n-type** semiconductor  $(\Phi_m < \Phi_s)$

#### **Metal-Semiconductor junction**

3-3. Summary of contact property of Metal-Semiconductor

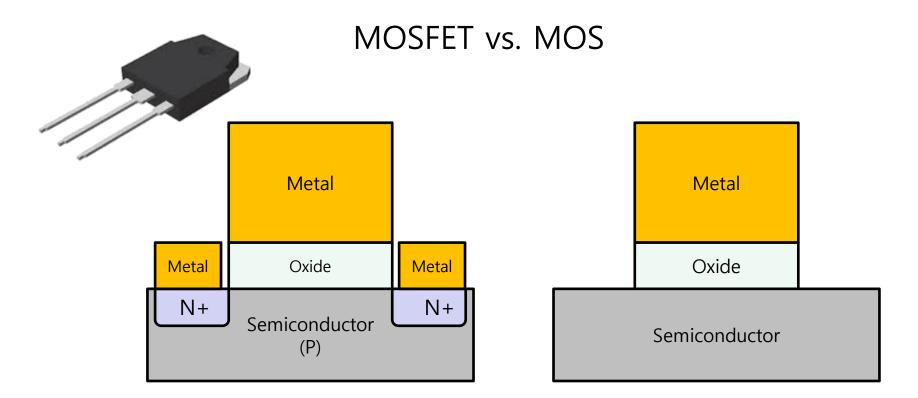

#### Metal-Oxide-Semiconductor

Applied Nanomaterials & Devices LAB. Electronics & Probes by Materials Engineering

MOS = Metal - oxide - Semiconductor

To understand the operation of MOSFET, we need to learn about MOS structure!

**Homework** What is the difference between MOSFET and <u>TFT</u>?

Channel: Organic, Oxide, 2D, Perovskite

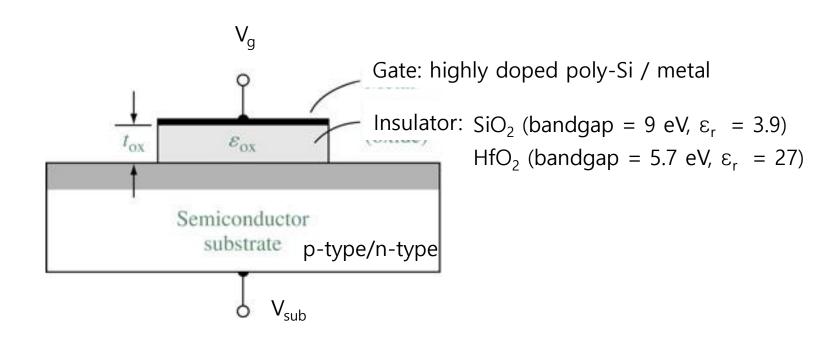

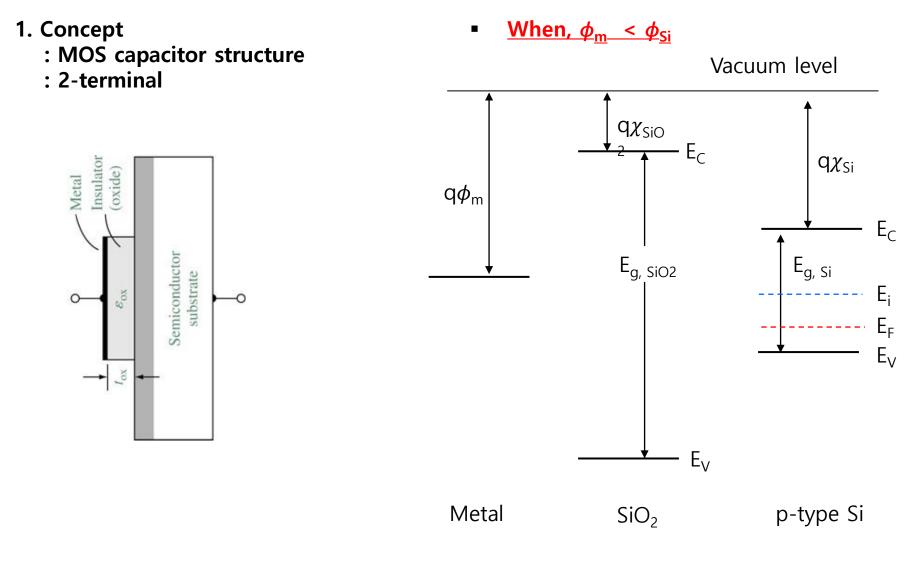

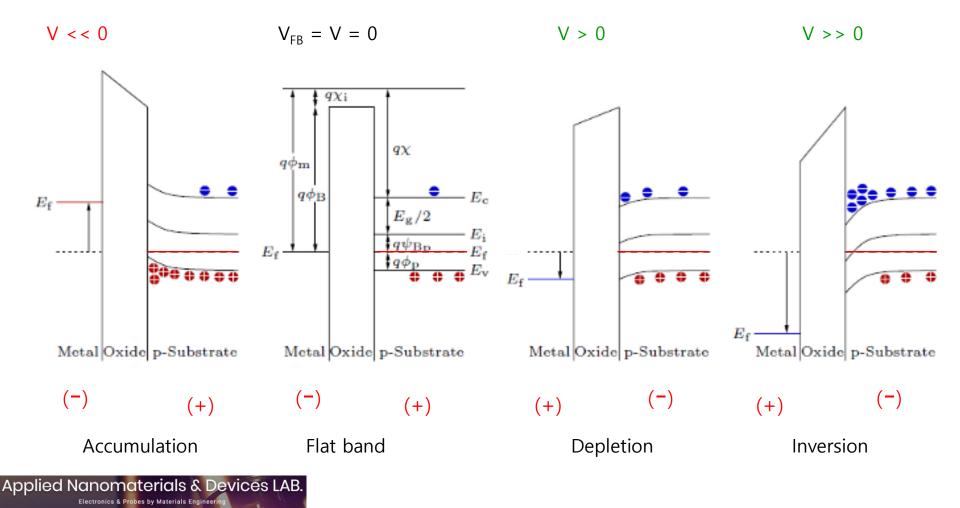

- 1. Concept

- : MOS capacitor structure

- : 2-terminal

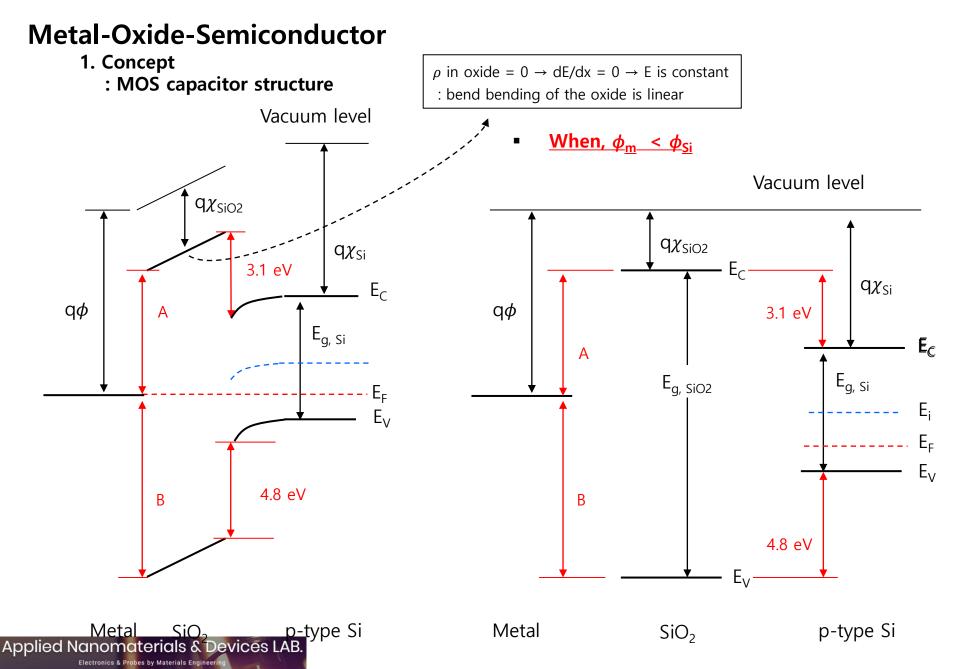

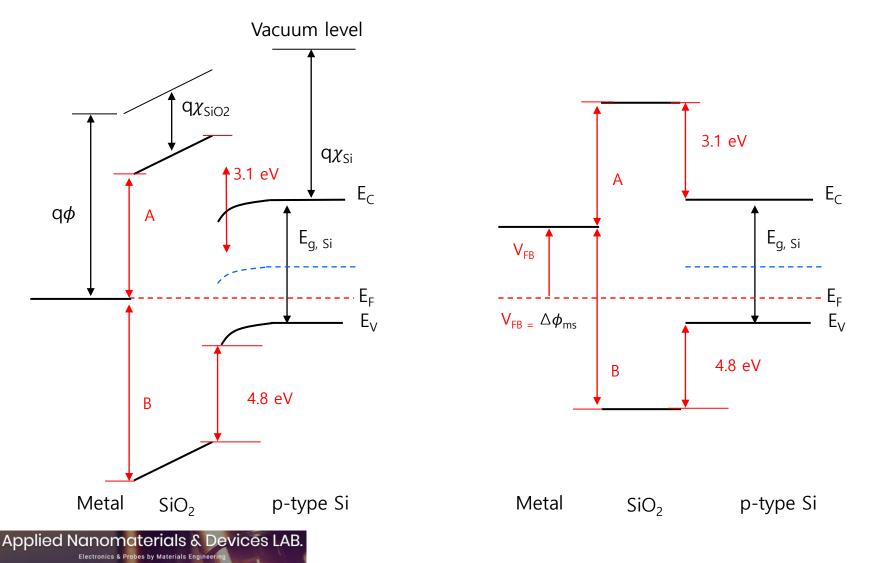

- 1. Concept

- : Flat band voltage the applied gate voltage such that there is no band bending in the semiconductor

- 1. Concept

- : MOS capacitor structure

- When,  $\phi_{\rm m} < \phi_{\rm Si}$

- 1. Concept

- : MOS capacitor structure

- <u>When,  $\phi_{\rm m} < \phi_{\rm Si}$ </u>

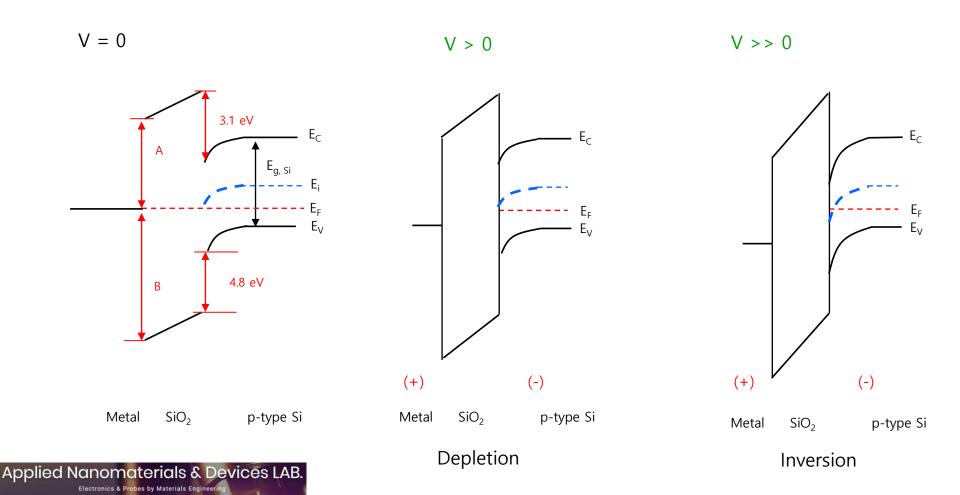

- 1. Concept

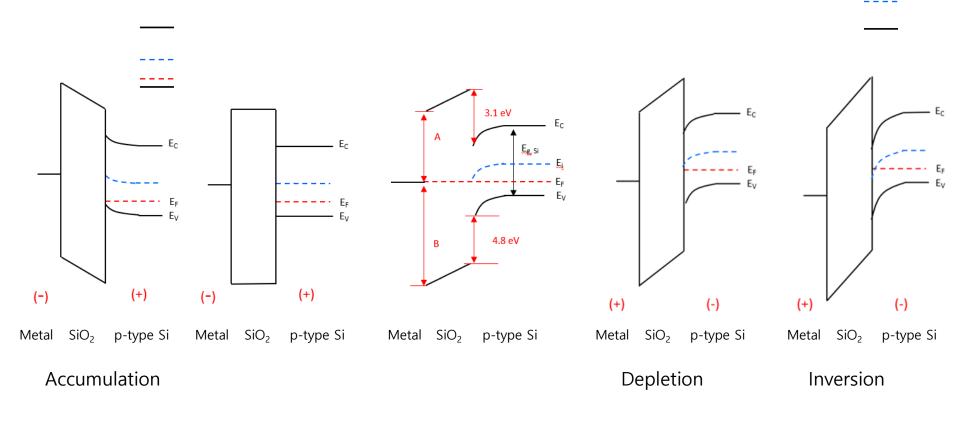

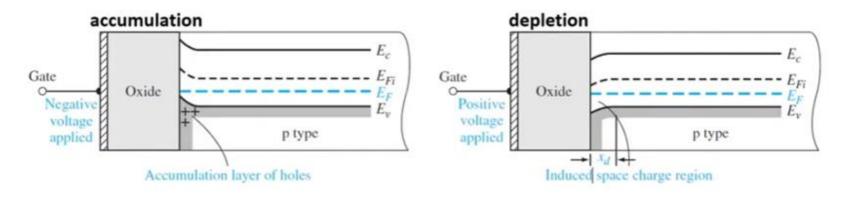

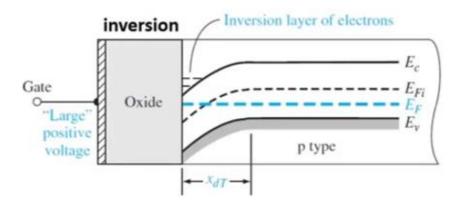

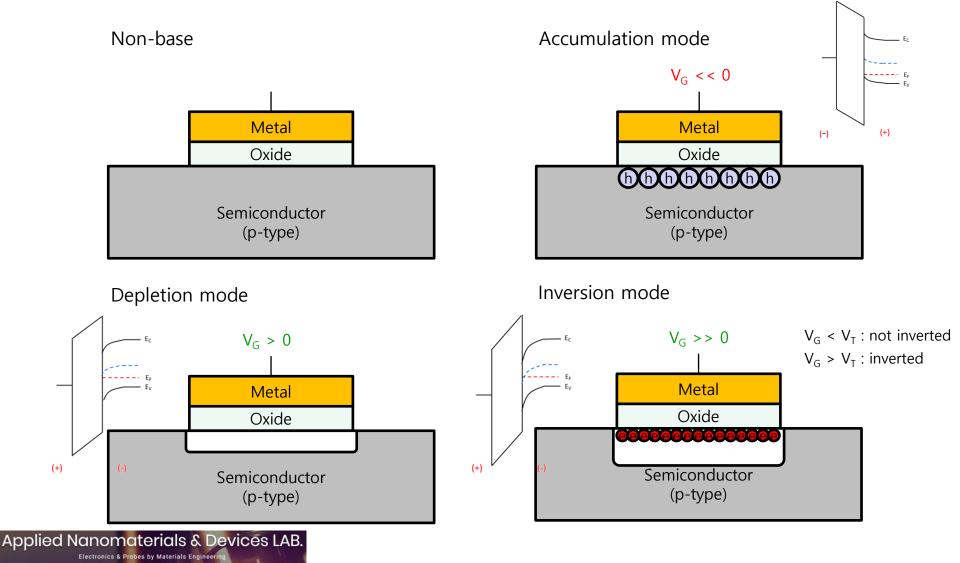

- : Operation modes

- When,  $\phi_{\rm m} = \phi_{\rm Si}$

- 1. Concept

- : Operation modes

- When,  $\phi_{\underline{m}} > \phi_{\underline{Si}}$

- 1. Concept

- : Operation modes

#### **Metal-Oxide-Semiconductor**

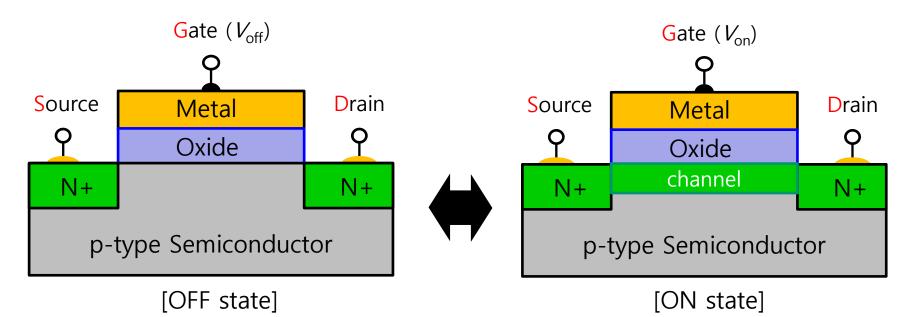

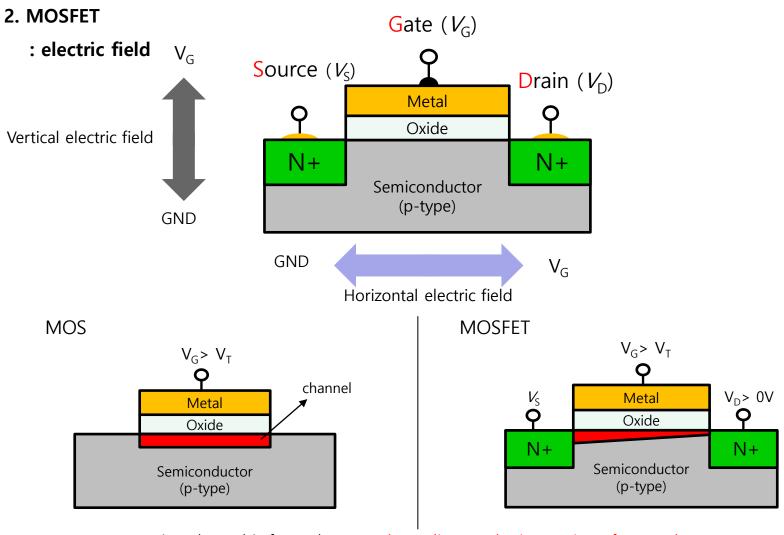

2. MOSFET

How to switch the FET?

- Transistor is <u>semiconductor</u> device used to <u>switch (or amplify)</u> electronic signals and electric power using <u>electric field</u>.

A: The gate controls the flow of current from the source to the drain electrodes by <u>formation of channel</u>

#### **Metal-Oxide-Semiconductor**

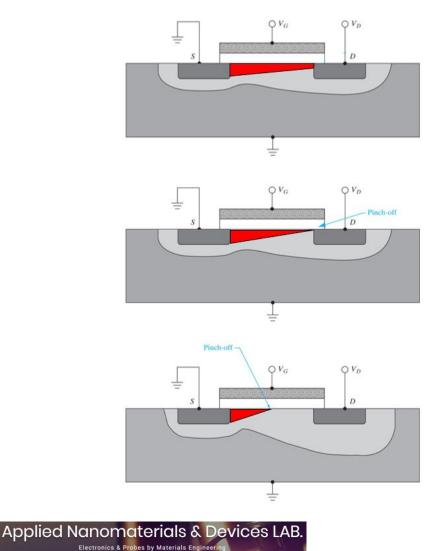

- Inversion channel is formed or not, depending on the interaction of  $V_{GS}$  and  $V_{GD}$

- The depth of the formed channel varies depending on the location

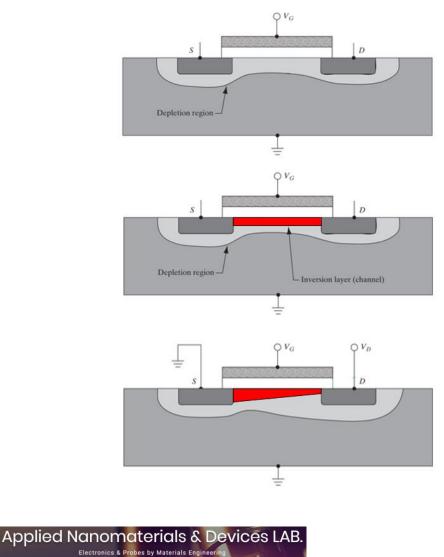

#### Metal-Oxide-Semiconductor 2. MOSFET

2-1. Operation process

$V_{S} = V_{D} = GND$  $V_{G} < V_{T}$ : accumulation or depletion state

$$V_{S} = V_{D} = GND$$

$V_{G} > V_{T}$  : Inversion state

$V_{S} = GND$ , low  $V_{D} > 0V$  $V_{GS} > V_{T}$  : Inversion state  $V_{GD} > V_{T}$  : Inversions state

Channel is formed in all area between S/D  $V_D \uparrow > I_{DS} \uparrow :$  Linear region

#### **Metal-Oxide-Semiconductor**

- 2. MOSFET

- 2-1. Operation process

$V_{S} = GND$ , low  $V_{D} > 0V$  $V_{GS} > V_{T}$  : Inversion state  $V_{GD} > V_{T}$  : <u>Inversions state</u>

$V_{S} = GND$ , Mid.  $V_{D} > 0V =$  pinch off voltage  $V_{GS} > V_{T}$  : Inversion state  $V_{GD} = V_{T}$  : <u>Pinch-off state</u>

$V_{S} = GND$ , High  $V_{D} > 0V$  $V_{GS} > V_{T}$  : Inversion state  $V_{GD} > V_{T}$  : <u>Depletion state</u>

Channels is partially formed between S/D  $V_D$   $\uparrow$  > maintain  $I_{DS}$  : Saturation region

#### Metal-Oxide-Semiconductor 2. MOSFET

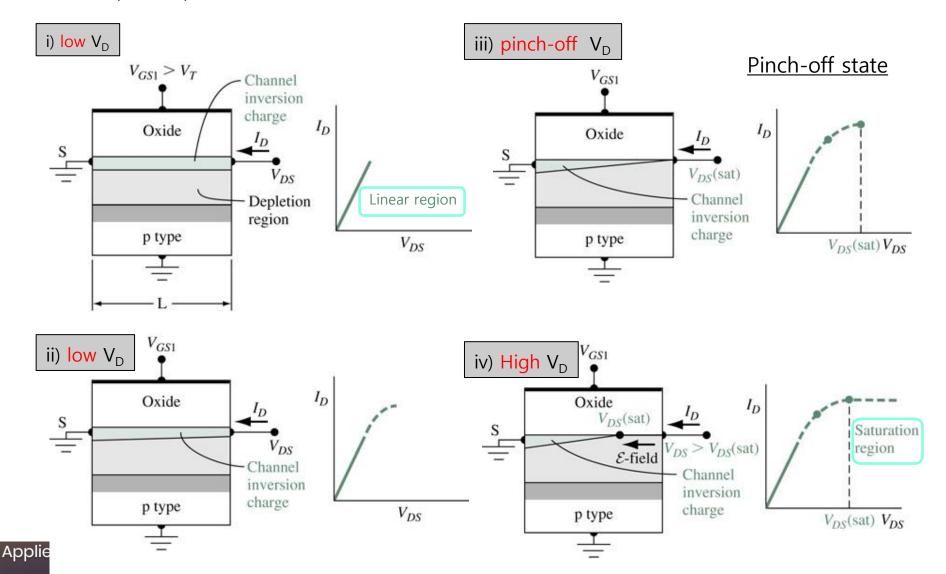

2-1. Operation process ( $V_{GS} > V_T$  : Inversion state)

#### **Metal-Oxide-Semiconductor**

#### 2. MOSFET

- 2-1. Operation process

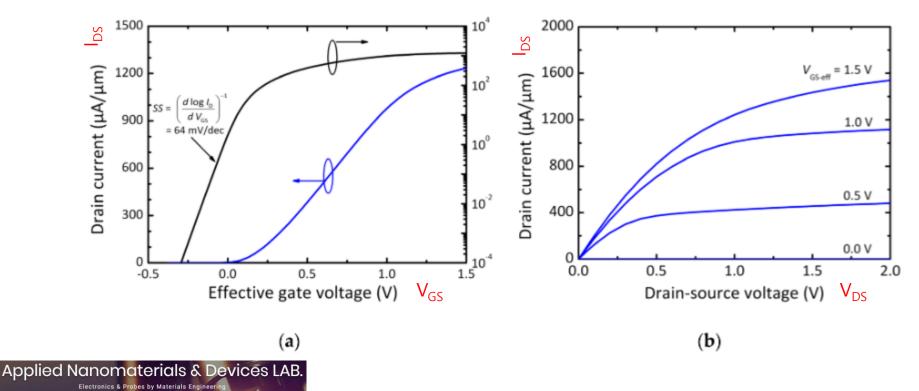

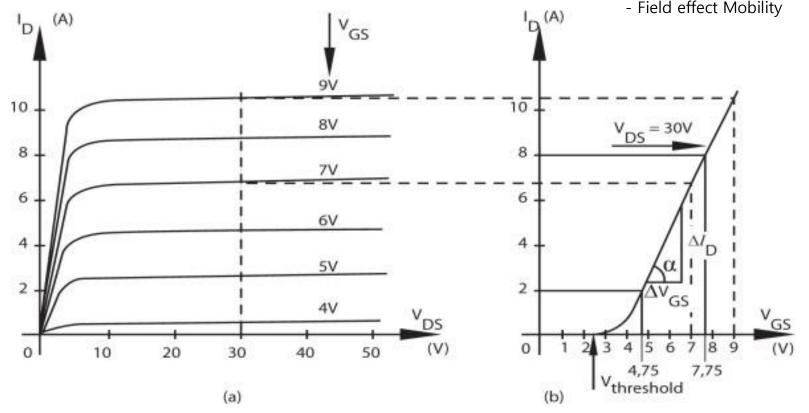

- : Output characteristic ( $V_{DS} I_{DS}$  curve)

**Figure 5.** Steady-state characteristics of the simulated 50-nm gate single-channel GNR MOSFET: (a) transfer characteristics; and (b) output characteristics.

#### **Metal-Oxide-Semiconductor**

#### 2. MOSFET

- 2-1. Operation process

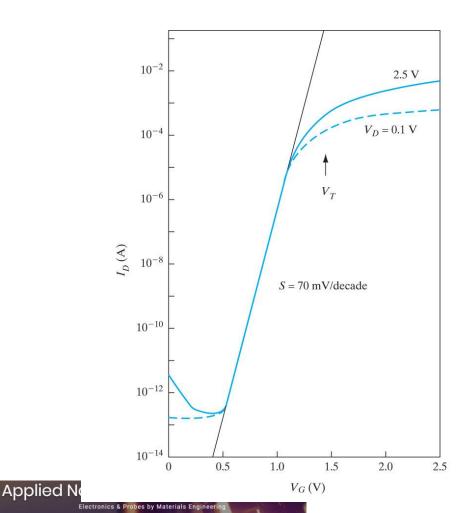

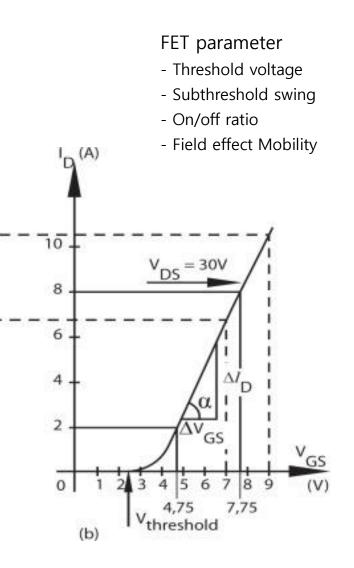

- : Transfer characteristic (V<sub>GS</sub>  $I_{DS}$  curve)

- Threshold voltage

- Subthreshold swing

- On/off ratio

- Field effect Mobility

#### **Metal-Oxide-Semiconductor**

#### 2. MOSFET

- 2-1. Operation process

- : Transfer characteristic (V $_{\rm GS}$   $\rm I_{\rm DS}$  curve)

#### **Metal-Oxide-Semiconductor**

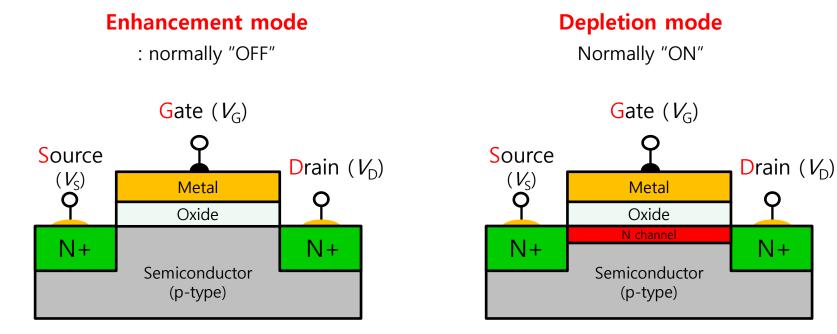

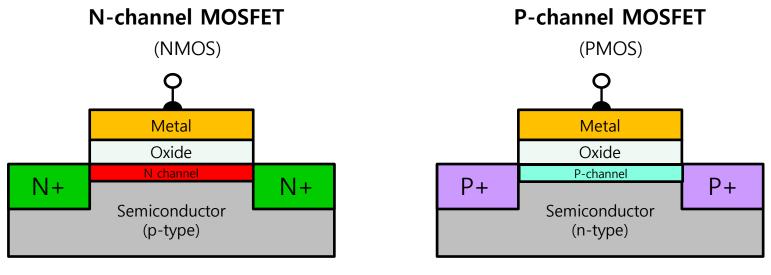

- 2. MOSFET

- 2-2. Types of MOSFET

No channel when  $V_G = 0 V$

Conductivity at channel area **is enhanced** by applying a gate voltage

Channel when  $V_G = 0 V$

Conductivity at channel area **is depleted** by applying a gate voltage

#### **Metal-Oxide-Semiconductor**

- 2. MOSFET

- 2-2. Types of MOSFET

$V_{GS} < V_T < 0V$

NMOS & PMOS operate in a complementary manner

$0V < V_T < V_{GS}$

"CMOS" = Complementary MOS

for constructing integrated circuit (IC) chips, including

microprocessors, microcontrollers, memory chips, and other digital logic circuits.

### End of Slide